# Using Existing Programmers to Program Low Voltage EPROMs

#### INTRODUCTION

The range of EPROMs manufactured by Fairchild Semiconductor is one of the largest in the industry. Fairchild's new family of Low Voltage EPROMs, targeted for power supply voltages in the range of 3V–3.6V, constitute a recent addition to the growing family of EPROMs. These Low Voltage EPROMs are 1 Mbit in byte and word-wide organizations. EPROM programmers currently available are designed to program the standard EPROMs which operate at 5V. With the introduction of Low Voltage EPROMs, most of the major manufacturers of EPROM programmers have begun the process of upgrading their hardware and software to accommodate the Low Voltage EPROMs. This issue of programmer updates is common to all manufacturers of Low Voltage EPROMs across the industry.

Fairchild's Low Voltage EPROMs can use exactly the same programming algorithm as the standard 5V parts and are fully capable of programming on existing programmers, which program the standard 5V EPROMs, with no adverse effects whatsoever on their reliability and endurance. This note seeks to alleviate any concern the EPROM user may have on programming the Low Voltage EPROMs on programmers which program 5V parts and shows that these programmers are guaranteed to correctly program Fairchild's Low Voltage EPROMs. We recommend using Fairchild's LV Turbo Algorithm. This will also check LV operation during programming operation. Beginning with a brief and simplified overview of the internal structure of EPROM, the note describes the process of programming and programming verify and shows that Fairchild's Low Voltage EPROMs program correctly on existing programmers.

## **EPROM OVERVIEW**

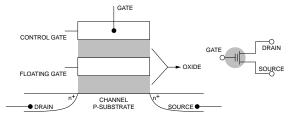

The basic storage element in the EPROM is a MOS transistor which has an additional "floating" gate built in between the control gate and the channel. This element is usually referred to as the cell (Figure 1).

FIGURE 1. EPROM Cell and Its Schematic

An important parameter of the cell is its threshold voltage —the control gate voltage at which the cell begins to conduct. The threshold voltage of an erased cell is well below the  $V_{\rm CC}$  value. When the control gate is driven to  $V_{\rm CC}$ , the erased cell conducts and this is a logic "1". Programming elevates the threshold of the cell by 5V–10V. This results in the programmed cell not conducting under normal operating voltages, and is permanently off. This is a logic "0". A fully erased EPROM reads all "1"s. Programming consists of applying elevated voltages to the gate and the drain of the cell. This causes electrons to penetrate the intervening oxide

# Fairchild Application Note 825

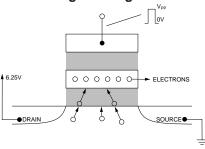

and deposit themselves on the floating gate (Figure 2), thereby altering the threshold voltage of the cell. This process is called "hot electron injection." The shift in the threshold, as already indicated, is typically 5V–10V.

FIGURE 2. Programming an EPROM Cell

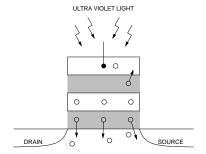

Erasure consists of shining ultra violet light on the die through the quartz window provided. This light provides the electrons trapped on the gate with sufficient energy to return to the channel and on to the control gate, and thereby returns the cell to the unprogrammed state. This is illustrated in Figure 3.

FIGURE 3. UV Light Erasure of Cell

The number of electrons that get liberated depends on the intensity of the light and the duration of exposure. As already noted, then new Low Voltage EPROMs from Fairchild use exactly the same programming algorithm as the standard 5V parts.

#### **PROGRAMMING**

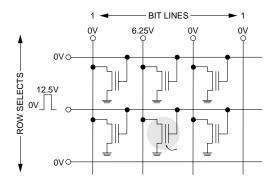

The programming algorithm specified by most manufacturers consists of programming data into the EPROM at the specified elevated voltage into all the locations that need to be programmed followed by a verify under normal read conditions. Programming the desired cell requires that an elevated voltage be applied to the bit line. The internal logic applies a high voltage pulse of 13V to the control gate in response to the external PGM pulse. This is illustrated in Figure 4.

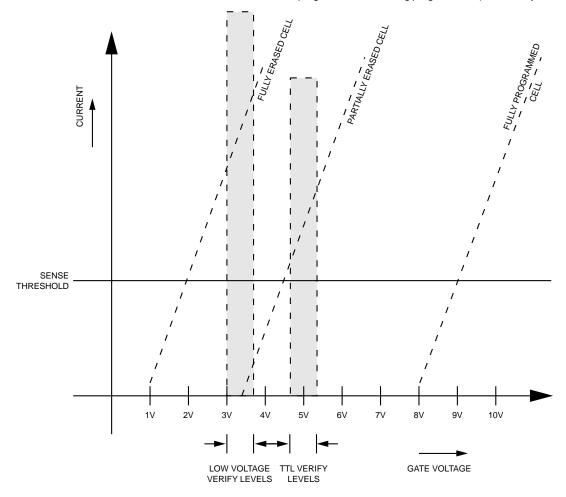

The verify is a "read" on the location to check if the cell has the right programmed state and margin. Internally a check is made to see if the cell conducts current of a magnitude greater than half the current of an unprogrammed reference cell. This reference value is called the sense threshold. Figure 5 depicts the relationship between the applied gate voltage and the current the cell con-

FIGURE 4. Programming a Cell in the Array

ducts. The amount of current a cell conducts depends on the threshold voltage of the cell and the magnitude of the voltages applied on the control gate and the drain.

#### PROGRAMMING VERIFY

An accurate verify must read the EPROMs at both  $V_{CC}$  (min) and  $V_{CC}$  (max). For the Low Voltage EPROMs the values are 3.0V and 3.6V respectively. Most of the current programmers perform verify

at the voltage levels specified for a standard 5V part. As a result of incomplete erasure, the lowered cell threshold voltage which might be adequate for 5V levels may not be so for low voltage operation. What this actually means is that the higher level of voltages (5V as against 3.0V-3.6V) may cause the cell to conduct current in excess of the sense threshold. When the voltages are lowered to the correct values, the cell current might not exceed the sense threshold. This is illustrated in Figure 5. When the partially erased cell is verified at 5V levels, the current magnitude exceeds the internal sense threshold. However, it would not qualify when verified at voltage levels 3.0V-3.6V. Thus, a part which verifies correctly at 5V might not when operated at 3V. The inability to verify at V<sub>CC</sub> levels 3.0V-3.6V is a limitation of current programmers and most programmer vendors are in the process of coming up with updates on their products which program and verify the low voltage parts correctly.

### PROGRAMMING LOW VOLTAGE EPROMS

Fairchild's Low Voltage EPROMs are also capable of functioning at the standard supply voltage (VCC) of 5V. Furthermore, Fairchild's proprietary manufacturing process using the split-gate SVG technology guarantees that the threshold of factory shipped parts are well below the 3V level and hence may be directly programmed on existing programmers (which verify at 5V levels).

FIGURE 5. EPROM Cell Characteristics

## **Life Support Policy**

Fairchild's products are not authorized for use as critical components in life support devices or systems without the express written approval of the President of Fairchild Semiconductor Corporation. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Fairchild Semiconductor Americas Customer Response Center Tel. 1-888-522-5372 Fairchild Semiconductor Europe Deutsch Tel: +49 (0) 8141-6102-0 English Français Italiano +44 (0) 1793-856856 +33 (0) 1-6930-3696 +39 (0) 2-249111-1 Fairchild Semiconductor Hong Kong 8/F, Room 808, Empire Centre 68 Mody Road, Tsimshatsui East

Kowloon. Hong Kong Tel; +852-2722-8338 Fax: +852-2722-8383

Fairchild Semiconductor Fairchild Semiconductor Japan Ltd. 4F, Natsume Bldg. 2-18-6, Yushima, Bunkyo-ku Tokyo, 113-0034 Japan Tel: 81-3-3818-8840 Fax: 81-3-3818-8841

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.