# **Introduction**

The Motorola/Freescale HC11 family MCUs are high performance 8-bit microcontrollers with enhanced architecture and extended instruction set. Providing that intended *target system (application with embedded target MCU)* meets some circuit design requirements, these MCUs can be ISP programmed. **You should be familiar** with the device to know its operation and features before you start working with it.

In-system programming of HC11 MCU is performed while operating in special "Bootstrap mode". This mode is entered after MCU reset, providing the MODA, MODB pins are at stable L level. *EXTAL* input is connected to external clock generator. External programming voltage is applied to Vpp/XIRQ\ input. Vpp value is set to 5V in case of programming and erasing any EEPROM memory area, 12V while programming an EPROM area. SCI pins *RxD*, *TxD* are used for serial communication. *VDD* and *VSS* are used to connection of supply voltage.

For detailed informations about all MCU configurable features, please refer to technical specification of programmed MCU – *Datasheet (DS)*.

#### Signals:

| Pin name   | Function      | Description                            | Signal level                            |

|------------|---------------|----------------------------------------|-----------------------------------------|

| VDD        | power         | supply voltage                         | 5 (V)                                   |

| VSS        |               | ground                                 | 0 (V)                                   |

| Vpp/XIRQ\  | control       | programming/interrupt<br>voltage input | L, 5 <sup>1</sup> , 12 <sup>2</sup> (V) |

| EXTAL      |               | external clock input                   | H, L                                    |

| MODA/LIR\  |               | mode select input/debug output         | L                                       |

| MODB/Vstby |               | mode select/standby input              | L                                       |

| RESET\     |               | MCU reset input                        | H, L                                    |

| RxD        | communication | SCI receiver, PD0                      | H, L, Pull-Up                           |

| TxD        |               | SCI transmitter, PD1                   |                                         |

<sup>1</sup>- voltage of 5V is applied in case of programming any EEPROM memory area.

<sup>2</sup>- voltage of 12V is applied only in case of programming EPROM/OTPROM memory area.

Table 1. HC11 MCU ISP related signals description

# Adaptation of target system for ISP

Following text contains **important notices** relating to correct ISP connection of in-system programmed MCU.

Respecting this, may prevent you from undesirable signal interference on pins *RxD*, *TxD*, *Vpp* of programmer and target system which often results in unsuccessful course of ISP operation.

Detailed information about ISP pin-driver capability and pins assign is listed in control program **PG4UW** of programmers (*Figure 6*).

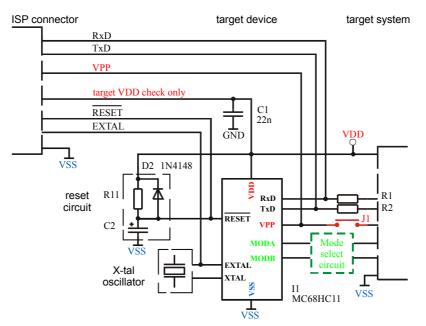

Figure 12. Circuit design

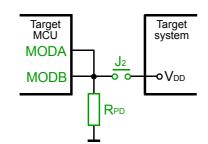

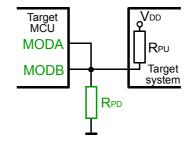

**MODA/LIR\, MODB/VSTBY** – Mode selection pins. They have to be in stable "L" level, during reset of MCU. It means, that voltage value mustn't exceed range <VSS-0.3V;0.2xVDD>. Mode select circuit should be adjusted accordingly to this condition. If the target system has even one of these pins directly connected to VDD, it's needed to disconnect it, and use weak Pull-Down resistor (*case 1, see Figure 13*). Other case, if these pins have a Pull-Up, your Pull-Down during ISP operation must be stronger, to meet previous declared condition, without disconnecting Pull-Up (*case 2, see Figure 14, Formula 1*).

ELNEC

Figure 13. Mode selection, case 1

Formula 1-4. Understanding the relationship between  $R_{PD}$  and  $R_{PU}$ , case 2

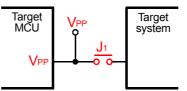

**VPP/XIRQ**\- MCU programming voltage input signal. Also marked as XIRQ\. Be aware, that voltage of 12V is applied to this pin, but only during programming any EPROM area. Isolation circuit should be designed according to this. In case of programming EEPROM, serial isolating resistor could be sufficient. For EPROM programming, it is better to use jumper, rather than resistor.

**Warning!** Higher voltage during EPROM programming could harm your target system. All of these operations and target system adjustments are made on your own risk. We are not responsible of any damages in target system.

Figure 15. Connecting programmers Vpp, isolation circuit

**EXTAL** – MCU clock input signal. This pin can be over-driven by a programmer's oscillator, even if a crystal resonator circuit or RC network is connected to the EXTAL and XTAL pins.

**RESET**\ – during ISP operation, the Reset pin is considered as input only, extended reset circuit (*RC integrating circuit*,  $R \ge 4,7k\Omega$ ,  $C \le 1\mu F$ ) may be used.

**RxD/PD0, TxD/PD1** – Communication pins, **TxD** of MCU is configured to standard CMOS output, **RxD** of MCU is configured as input, no Pull-Up resistor is needed during any ISP operation.

**VCC** – Power supply for programmed MCU must be derived from target system. The programmer uses this signal only to test, if the target MCU is powered. You can omit to connect this signal, and disable VCC sense.

**GND** – Common ground for programmer and target system.

# **Operating with device**

#### **Device operation options:**

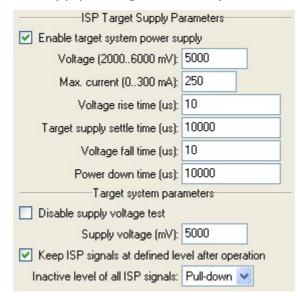

Most of the programmers offer an option to supply power for target system. If you want to use it, you must set up at least basic parameters. You can do it through menu *Device Options* <Alt+O> - in next <Alt+O> (see Figure 4).

Voltage level limitation of logical *H* signal is derived from target memory *VCC*, set in *Supply voltage* edit box (*value 3300mV*, *Figure 16*).

Figure 16. ISP target supply parameters setting <Alt+O>

For further description of ISP parameters, please take a look at menu *Help* by pressing the  $\langle F1 \rangle$  key, while the window  $\langle Alt+O \rangle$  is opened.

#### **Device info (Ctrl+F1):**

The following window contains reduced information from this application note and details about pins assign for each programmer with short description of circuit design (see Figure 6).

| Device info                                                              |                                                                                                  |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Common information ISP connection detail                                 | ails 🧧 Part number description                                                                   |

| ISP Note: The programmer is workin                                       | Device info                                                                                      |

| operation can be made through ISP                                        |                                                                                                  |

| The ZIF socket of the programmer m                                       | Common information ISP connection details Part nu                                                |

| forgotten in the ZIF socket, might                                       | Manufacturer: Motorola                                                                           |

| ISP connector of BeeProg programme                                       | Type: MC68HC11E9 (ISP)<br>8-bit bytes: 10000h                                                    |

|                                                                          | Organization: 10000hx8 bit                                                                       |

| 2 4 6 8 10                                                               | Algorithm name: Specialized                                                                      |

| 2- 4- 6- 8- 10-                                                          | Summont of Bur                                                                                   |

| 1 3 5 7 9                                                                | Supported By:<br>BeeProg (Note: via ISP connector)                                               |

|                                                                          | → JetProg (ISP module (ord.no. 70-0217))                                                         |

| Inside look into the BeeProg progr                                       | - Secritog (137 module (SI4.16. 75-5217))                                                        |

| connector signals:                                                       | General Info:                                                                                    |

| C1                                                                       | CONFIG register is located in buffer on the ad<br>EEPROM array is located in buffer from B600H t |

|                                                                          | ROM array is located in buffer from DOCOH to F                                                   |

| H/L/read driver R1                                                       | Reading of ROM array must be enabled in menu "                                                   |

|                                                                          | For better explanation and further information                                                   |

| PU/PD driver R2                                                          | please, visit our web site, and download corre                                                   |

| in programmer                                                            | Decertification of TCP                                                                           |

| Cl lnF, Rl 1k3, R2 22k                                                   | Description of ISP connector pins:<br>1 - Target VDD sense                                       |

| The choice portioned velues are pre-                                     | 2 - TxD                                                                                          |

| The above mentioned values are pro<br>calculate) the value of resistors, | 3 - RESET\<br>4 - EXTAL                                                                          |

| (separate) the programmed chip and                                       | 5 - Target System Supply Voltage                                                                 |

| Recommended target circuit design                                        | 6 - RxD                                                                                          |

| Accombined enget circuit design                                          | 7 - GND<br>8 - Don't connect!                                                                    |

| ISP connector target                                                     | 9 - Don't connect!                                                                               |

| RaD<br>TaD                                                               | 10 - VPP/XIRQ\                                                                                   |

| VPP                                                                      | OK                                                                                               |

| target VDD check only                                                    |                                                                                                  |

| RESET                                                                    |                                                                                                  |

| EXTAL                                                                    | 22n                                                                                              |

| GND                                                                      |                                                                                                  |

| VSS D2 1N4148                                                            |                                                                                                  |

| reset R11                                                                |                                                                                                  |

| circuit , Ļ                                                              |                                                                                                  |

|                                                                          |                                                                                                  |

|                                                                          | MODA Mode Mode select                                                                            |

|                                                                          |                                                                                                  |

|                                                                          | 1 MC68HC11 VSS                                                                                   |

| v                                                                        | SS MC08HC11                                                                                      |

| R1, R2: 10k                                                              | <b>v</b>                                                                                         |

|                                                                          | ОК                                                                                               |

|                                                                          |                                                                                                  |

|                                                                          |                                                                                                  |

| Figure                                                                   | <i>17. Device info</i>                                                                           |

|                                                                          |                                                                                                  |

|                                                                          |                                                                                                  |

|                                                                          |                                                                                                  |

|                                                                          |                                                                                                  |

# **Used abbreviations**

**AN** – Application Note.

**CPU –** (Central Processing Unit).

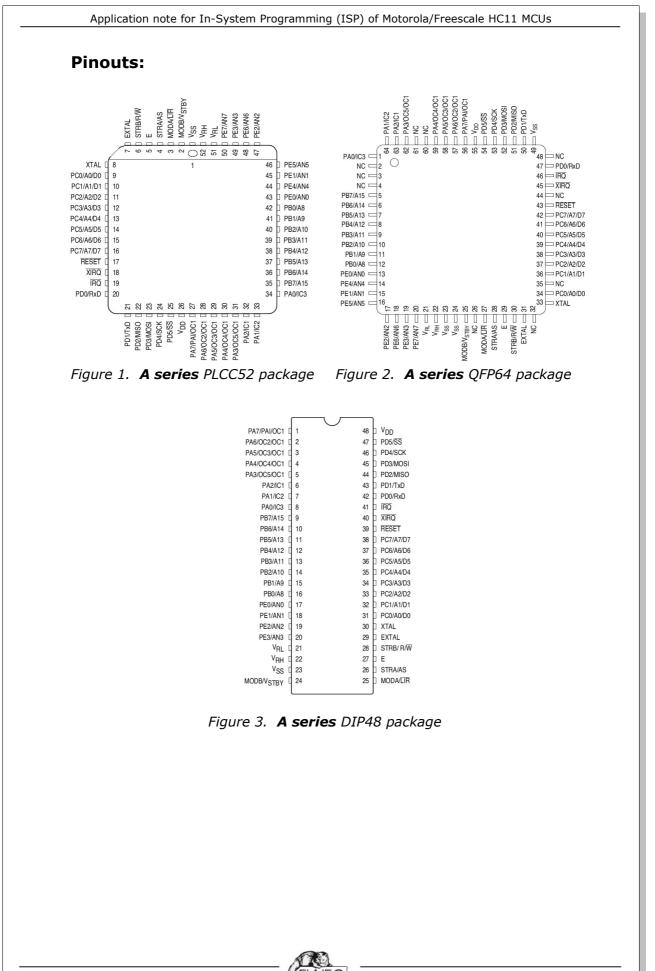

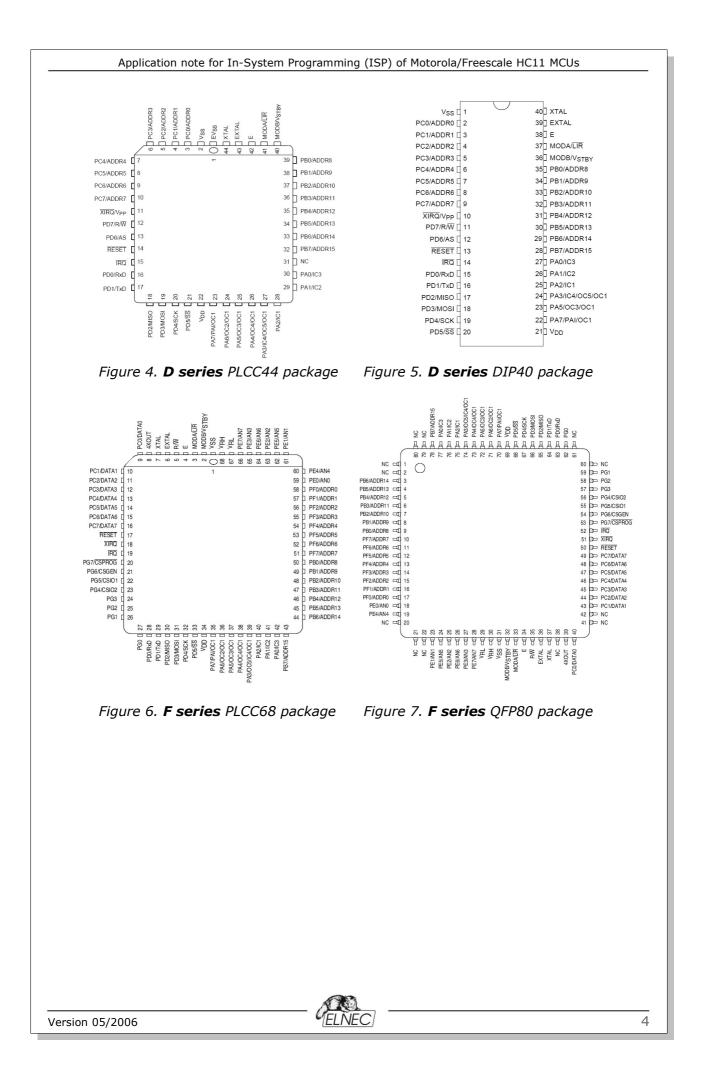

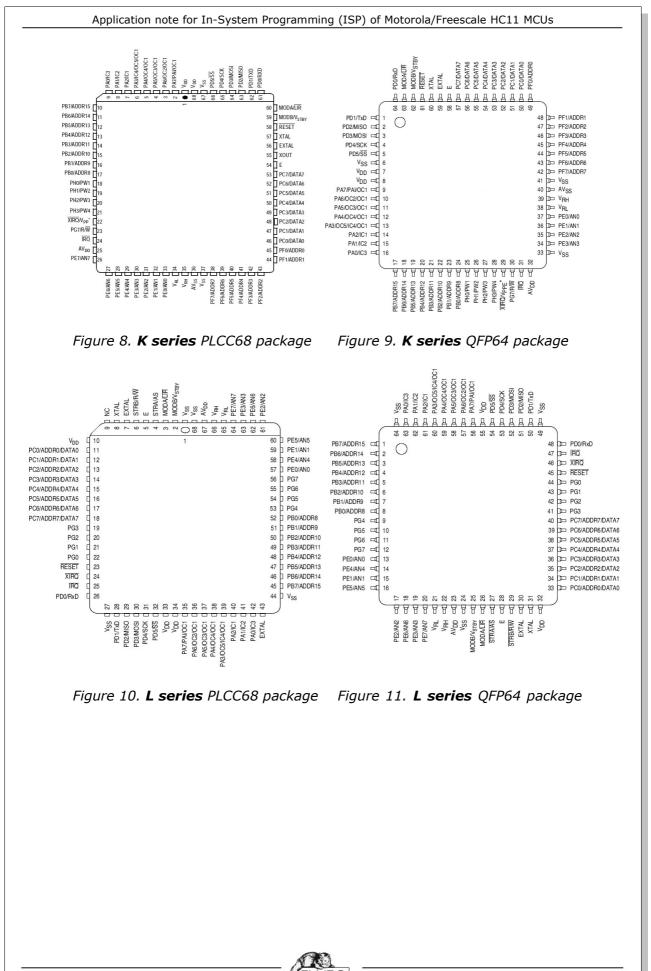

**DIP, SDIP, QFP, TQFP, PLCC** – type of device package.

**EEPROM** – (Electrical Erasable Programmable Read Only Memory) type of memory.

**EPROM –** (*Erasable Programmable Read Only Memory*) type of memory.

**ISP** – (*In System Programming*) programming of device inserted into system.

**MCU –** (*MicroController Unit*) *CPU with integrated peripherals and other features.*

**Open collector/drain** – type of used interface, collector/drain of transistor creates an output. In order to be output able to set H level, the device needs to be supplied with constant PU on the pin.

**Pull–Up (PU)/Pull–Down (PD) –** increase/decrease of signal level by connecting PU/PD resistor to VCC/GND.

**Target MCU –** MCU to be programmed via ISP.

**Target system –** *circuit, where the target MCU is embedded*.

**ZIF** – (*Zero Insertion Force*) type of socket, used in programmer for better manipulation with device.

# **Revision history**

### 05/2006:

Changes of figures:

- Fig. 12 Circuit design minor changes

- Fig. 17 Device info- minor changes

### 06/2005:

Initial Release.